(老冰翻译、整理并根据自己的理解改写)

光刻技术大概是现代集成电路的第一大关键技术。现在,液浸式光刻系统是最为成熟的技术,被认为在短时间内很难被取代。不过,极紫外光刻(EUV光刻)技术半路杀出,成为近年来三星、台积电等公司的追捧。有人认为EUV光刻能够拯救摩尔定律,但事实是否真的如此?

EUV实地测试:在位于纽约阿尔伯尼的纽约州立大学理工学院里,这台EUV光刻机(型号ASMLNXE:3300B)被用来刻出芯片表面的容貌。从图中这台设备前方的靠底部位置,可产生用来曝光晶圆表面的EUV光。机器远端连接了一条导轨,可以给晶圆在曝光前覆上涂层,并处理曝光后的工作。

你很难想象它有多大。纽约的价值120亿美元的GlobalFoundries制造中心成行成列地摆放着高大的机器。天花板上的轨道里,有装载晶圆的运输设备从头顶呼啸而过,就像倒挂的微型过山车。你可以在那里看到运输设备把晶圆装载到生产设备上,接下来是三个月的生产周期,设备把盘子大小的裸硅晶圆加工成可用在智能手机、电脑和服务器里面的芯片。如果在新年开始制作一个微处理器,可能要等到春天才能完成。

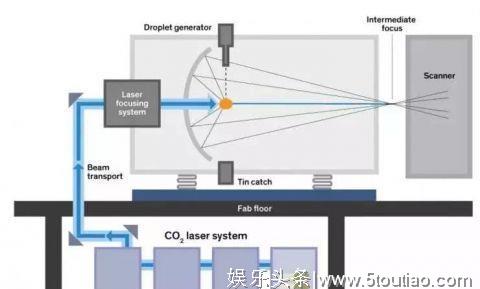

机器内部:EUV的产生,需要把二氧化碳脉冲激光发射到管道中,并在管道中与微型的锡液滴碰撞,进而产生等离子体。

这台位于ASML荷兰费尔德霍芬总部,经过特殊组装的EUV光刻机,是该公司最新的产品之一

在这种先进的制造过程中,一块晶圆要经历至少60次这样的过程:表面被覆上光刻胶,随后进入一个密闭的光刻机。激光会打在预制刻有线路的平板上,在晶圆表面投射出被缩小的线路。这样可以生成超精密的线路,也就是最先进的处理器的内部构造。

这些光刻机从和其他无数自动设备并无所不通,其实很难区别,也没有挂什么红色的标识牌标明“此处为重要工序”。但光刻就是工厂的心脏。

这些光刻机就在证明摩尔定律。在五十多年中,半导体工艺进步惊人,集成电路的半导体密度不断翻倍。数十年来,包含光蚀刻在内的一系列技术突破,使得芯片制造商可以不停地缩小芯片、缩短研发周期并,把更多晶体管放进芯片。这些进步使我们从上世纪七十年代那种几千个晶体管的芯片进步到了如今的几十亿个。

为了行业持续的良性发展,芯片界的领军公司们不能只依赖以往的高端光蚀刻技术。他们正试图进行一次重大的也是最具挑战性的转变。

从一开始半导体光蚀刻就是通过电磁波辐射,即光照来实现的。但在半导体企业现在看重的技术里,用了另外一种辐射,它的叫极紫外光(EUV)。与当前的光刻机不同,EUV无法在空气中传播,也不能通过透镜或者传统镜面聚焦。

EUV的产生也十分困难。首要的一步,是将激光照向一束快速射出的熔融态锡液滴流。此举是为了让制造出的光刻机能使用13.5nm波长的光,这样光刻机可一次完成以往需要多次曝光的蚀刻,从而节省成本。

在光刻机内部,为了实现EUV光刻,一系列反射镜可以把EUV辐射从光刻机的光源位置传输到光掩模板上。掩模板上带有需要蚀刻的线路,可将EUV传递到晶圆上。附加的导轨负责晶圆在光刻机的运入和运出。掩模板有自身独立的出入口。

但制作一个亮度和可靠性足够可靠,且能每天24小时全年不间断运行的EUV系统是一个工程难题。但荷兰的光刻工具制造商ASML控股生产的EUV光源已经在2018年开始了商业化投产,实现最新的微处理器和存储器的批量生产。世界最先进的芯片制造商都在努力将这些机器应用在自己的生产线中。

这样做的风险很高。没有人能确定去年总产值为3300亿美元的半导体产业在5年或是10年后的发展,也无人知晓“后摩尔定律”时代的半导体行业会是什么样子,甚至连利润的下降都可能是无法避免的。

光刻系统的精细程度取决于很多因素。但最有效的方法是降低使用光源的波长。几十年来光刻机制造商们就是在这么做,他们将晶圆曝光工具从人眼可见的蓝光端开始逐渐减小波长,直到光谱上的紫外线端。

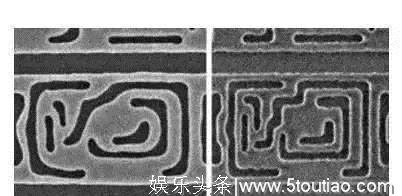

图中是ASML公司产品上的曲线和折角。EUV与现在使用的193nm光源的多重成像技术(左)相比,保证了产品有更加尖锐的形状(右)。图中线的最小宽度为24nm。

80年代后期,半导体行业用激光代替汞灯,将波长从365nm降低到248nm。日本电信公司NTT的在1986年发表了使用11nmX射线的结果。AT&T公司的贝尔实验室和LawrenceLivermore国家实验室也分别实践了这种技术。1989年,一些相关研究学者在光蚀刻学术会上碰面并交换了研究思想。再后来,相关的研究开始得到国家和行业内的赞助。

90年代后期,ASML公司和其他一些合作伙伴开始研究EUV光刻技术,十年之后,ASML公司实现了一个EUV光刻机样机,使其他研究者们可以测试这种方法。

但是,EUV技术是非常困难的。在使用波长近乎为X光的射线去蚀刻时,物理学知识并不能帮上多少忙。对于公司最终选择的13.5nm波长射线,这种光可以轻易地被很多材料吸收。所以EUV光刻机只能在真空下运行,晶圆通过一个气闸进出光刻机。

EUV也能被玻璃吸收,所以在机器中改变其走向只能用反射镜而不能用透镜,还不能是普通的反射镜。普通反射镜面的反射率不够,必须使用布拉格反射器(Braggreflector,一种多层镜面,可以将很多小的反射集中成一个单一而强大的反射)。

ASML的EUV机器里的镜面由40对交叠的硅片和其上覆盖的钼层组成,每一层只有几纳米厚。蔡司公司制造了这些镜面,他们非常精确地加工了这些非球面表面。但即便一切都做的非常完美,也就只能得到70%的反射率。就是说光源通过该系统中的每一对镜面时都会减少1/3。光刻机在把EUV光线从光源照射到掩模板上的时候,要用到好几个镜面,而掩模板本身也是一个镜面,经过它光线才会照到晶圆上。所以一个EUV光束在经过长途跋涉后,只有不到2%的光线能保留下来。

到达晶圆的光线越少,晶圆在光刻机中曝光的时间就越长。然而时间就是金钱。为了弥补镜面反射过程中的损耗,射线光源必须非常强。这一点在实践中也被证明了。

在研究早期,EUV研究者甚至使用了粒子加速器。但是最有效且经济的得到足够亮度的方法是用等离子体。使用正确的材料和足够强的激光器或电流,就可以将电子从其附着的原子中分离出来。由此产生的等离子体在从超热滴状态冷却到之前的稳定状态过程中就会发生EUV辐射。

但是这种技术的进展一直很缓慢,光照亮度的提升始终未尽人意。直到2011年,总部在圣迭戈的世界领先的光源制造商Cymer才成功地制作出一个能持续使用的光源。ASML公司在2013年用31亿欧元收购了Cymer。

为了制作EUV光,Cymer使用了一种叫做“激光等离子体”的方法,这种方法是在一个真空腔体中,用源自金属切割技术的放大器,产生强大的二氧化碳激光,通过腔体,照射一束每秒被发射出5万滴的超纯锡液滴。当激光脉冲照射到锡液滴时,液滴会被加热成等离子体并产生EUV射线。接着,一个反射镜收集器将该过程产生的光线反射到光刻机中。因为这种方法在产生EUV光时也产生了锡碎片,所以还要持续为反射镜收集器喷射氢气,以保证它不会被一层锡所覆盖。

没有人质疑EUV机器能实现的高精度。你在半导体行业大会上经常会看到一些展示,将EUV技术制作的清晰微小线路和目前传统技术做出的模糊线路进行比较。

但是现在的问题是,EUV在芯片的批量生产中会扮演怎样的角色?采用EUV技术的成本会很高。最新EUV机器的价格超过1亿欧元,是现有常规光刻机价格的二倍多,机器的大小相当于一辆大巴士,需要用多台747飞机运输。该机器要消耗1.5兆瓦的电力,远超现有的机器。

ASML液滴的进化:为了生成EUV光,熔融的锡液滴被激光脉冲击中后,变得扁平;之后被激光二次击中,变成可以辐射EUV射线的等离子体。

这个技术的形成有两个主要的突破。第一个突破是浸液式光刻,即是将水放在晶圆和镜头之间。第二个突破是多重成像,即是将一层成像的过程分解成两步或多步。从原理上说,成像步数越多,成像越精密。但也就会使得制造成本更加高昂,工艺更加复杂。

GlobalFoundries在制作14nm级别芯片的时候,使用的是三重蚀刻法。也就是说,针对某些关键的芯片内层,芯片要经受光刻机和其他设备的两次额外蚀刻。他们计划在下一代7nm产品上使用四重光刻法。

EUV技术是否使用的关键点,就是它能否和多重光刻在成本上打个平手。这个问题很难回答,因为实际的成本取决于太多因素,比如EUV光源亮度和EUV光刻系统正常运行时间能达到怎样的程度等等。

MarkMontgomery/ASML锡动力:为了生成EUV,ASML的光源需要用脉冲激光,照射快速射出的锡液滴流。这个过程始于加工车间的地下,在里面可以生成两组激光脉冲。每个锡液滴先被一束预脉冲照射,变平;然后再由主脉冲照射,被加热后生成等离子体。装置里有一面收集反射镜,负责将生成的射线导入到光刻机中。

在EUV上面烧钱的除了GlobalFoundries和IBM之外还有英特尔、三星和台积电。对EUV技术下大手笔的原因不仅是因为技术本身的难度,更主要因为半导体厂商们坚信,没有EUV技术,他们会止步不前。如果你去问他们EUV对于摩尔定律的重要性时,他们一定会非常肯定地强调:“肯定重要。百分之一百重要。非常非常重要”,台积电甚至希望他们能在5年后在5nm工艺芯片生产线上使用EUV技术。

现在EUV还存在一些工程上的挑战。主要问题就是保护掩模板(像模板一样的平板,上面有待印刷的图案)。像光刻机里面的其他元件一样,掩模版也带反射性,棘手的反射系数又成了问题。

光刻机的掩模版由一层护膜保护着。这层薄膜距离掩模版有一点距离,像保鲜膜一样紧绷在上方。即便是一个肉眼看不见的小灰尘也可以影响几百个晶体管的曝光。如果有一粒灰尘落到了保护膜上,保护膜就会因为无法聚焦而不能在晶圆上形成图案。

而且这种护膜并不是为EUV所设计的。因为在这种波段下透明度不够高,EUV很快就会损坏护膜。ASML原计划制造不带护膜的光刻机,但是芯片厂商不同意,“如果一粒灰尘落到了掩模版上,晶圆上面的每一块晶片都会被损坏,最终良品率可能为零”,可能损失掉价值几万甚至几十万美元的芯片。

于是,ASML便开始研究能够抵抗EUV破坏的护膜。这种护膜的透光度必须尽可能地高,这样光源在到达掩模版的时候就可以几乎不发生损耗。这种情况下难度几乎翻了一倍:因为EUV的掩模版反射系数比透射系数要高,所以光必须穿过护膜两次:一次进入,一次反射出。

这项技术还包括一些其他的挑战。一个是制作无错的EUV掩模版,并用高效的方式验证这块掩模版是完美无暇的。另一个是光刻胶,它是一种光敏材料,被覆在晶圆表面,接收掩模版的图案。

现在使用的光刻胶,即化学放大光刻胶,由分子链聚合而成,可以增强入射光子的效果。但是这些材料对EUV的吸收效果并不好。此外,由于入射光引起的放大反应在材料内部散射,光刻胶形成的图像会有轻微模糊。为了能实现比当前技术更精细的线路图案,必须要有尺寸小得多而且更可靠的制造模块。新型光刻胶由更小的锡氧化物组成,吸收EUV的效果是之前的五倍,而且线路图案也不会受放大影响。

摩尔定律的命运不仅取决于芯片工艺的尺寸,也取决于物理学家和工程师对生产出的晶体管和电路可以改善到何种程度。即使从一束快速激射出的锡等离子体上发出的亮光也不能说明技术的发展会在何时终止。但它可能会为前程提供一点亮光。

翻译工作十分辛苦的